Medfield macht Intel in einem Smartphone salonfähig

- Intel: x86-Prozessoren fürs Smartphone

- Rechenleistung - Top-CPU und -Internet, mittelmässige GPU

- Medfield macht Intel in einem Smartphone salonfähig

- Android auf x86 mit Binärübersetzer für ARM-Code

Anbieter zum Thema

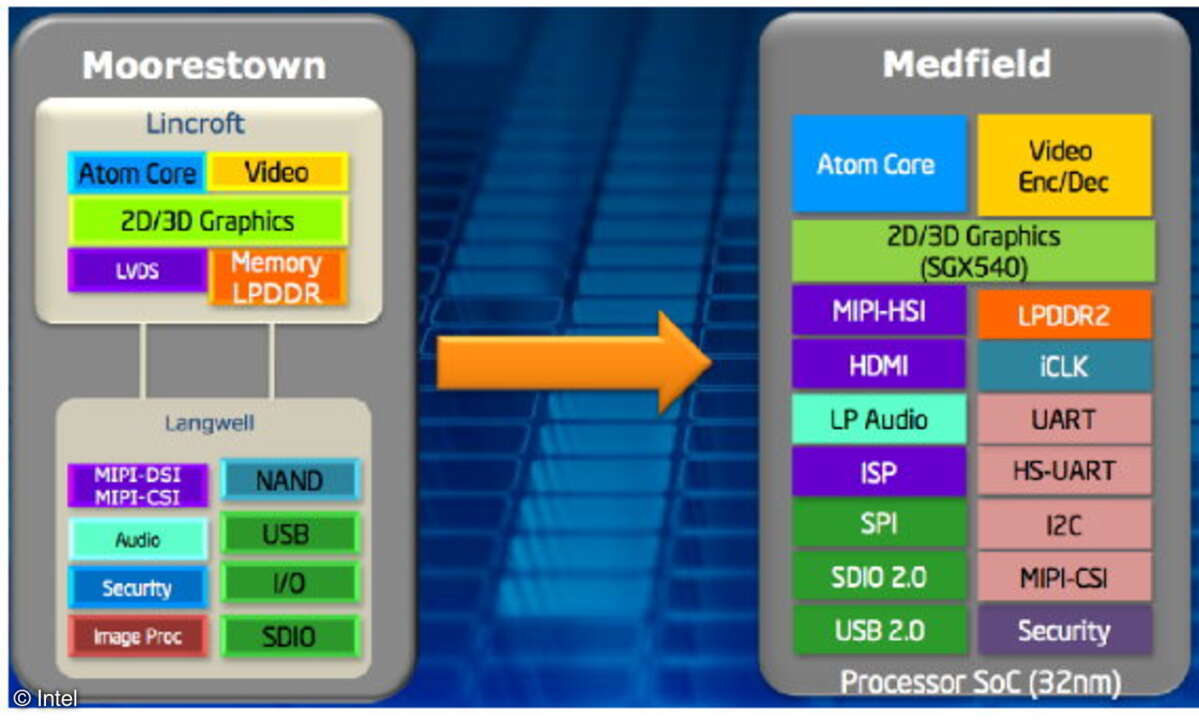

Die Vorgängerplattform "Moorestown" hat es nicht in ein Smartphone geschafft, was wenig verwunderlich war: Nicht nur, dass es sich um eine 2-Chip-Lösung handelte (Bild 1), nein, zusätzlich waren noch ein Power-Management-IC und externes DRAM erforderlich, und dies auch noch als LPDDR1 ausgeführt. Platzsparender PoP-Speicher (Package-on-Package) war nicht vorgesehen. Dass zusätzlich nur eine 5-MP-Kamera und lediglich 720p-Video-Encoding angeboten wurde, gab Moorestown den Rest.

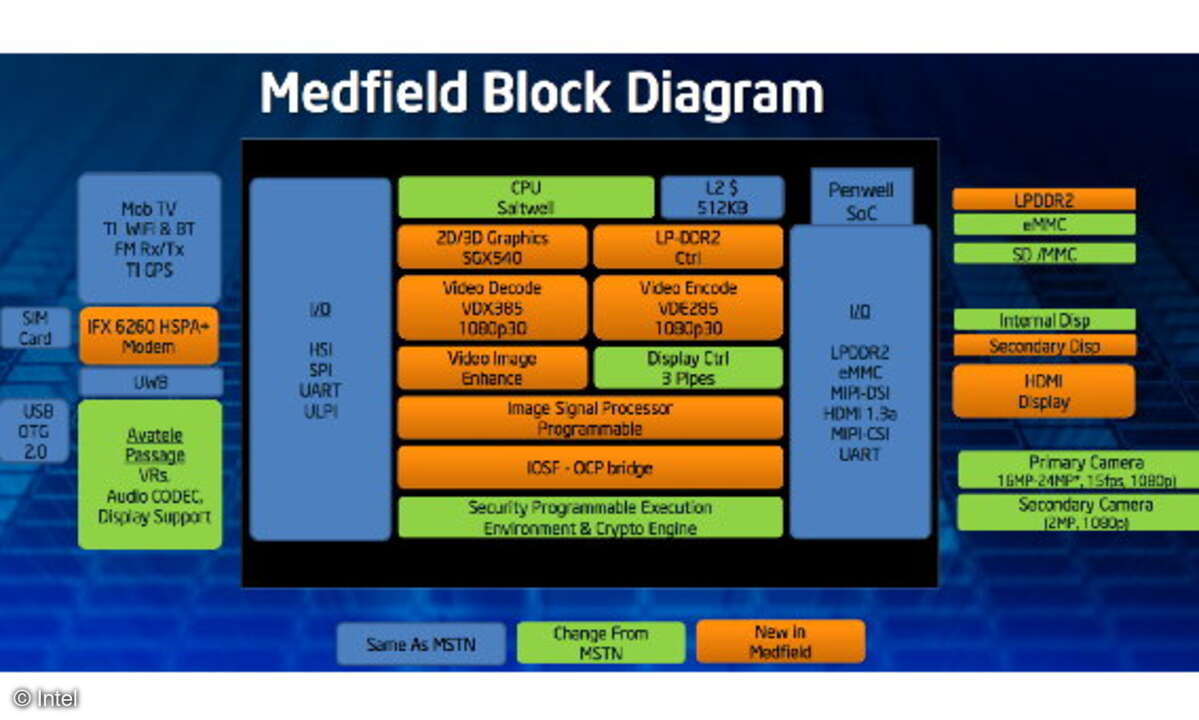

Mit Medfield erwies sich Intel als sehr lernfähig: Nicht nur die Integration der vormals in zwei Chips (Lincroft und Langwell, siehe Bild 1) aufgeteilten Funktionsblöcke sondern LPDDR2-PoP-Speicher (2x32-bit-Anbindung), ein aus Intels Kauf der Firma Silicon Hive resultierender Bildverarbeitungs-Prozessor der Spitzenklasse (ISP, dazu später mehr) und die Grfaik- und Video-IP von Imagination Technologies versetzten Intel in die Lage, eine Plattform wie der Wettbewerb anzubieten, bestehnd aus einem SoC, einem Power-Management-IC und PoP-LPDDR2. Bild 2 zeigt das Blockdiagramm von Medfield, abgesehen von der Satwell genannten CPU (einem Atom) sieht es einem ARM-basierenden SoC mehr als ähnlich.

Die Mikroarchitektur des Atom-Prozessors haben wir bereits kurz nach dem Erscheinen des ersten Derivates Ende 2008 hier ausführlich beschrieben. Der Saltwell genannte Atom-Core wird mit 1,6 GHz getaktet, hat 512 KB L2-Cache und eine 32 bit breite Dual-Channel-Speicheranbindung zum LPDDR2-Speicher. Saltwell hat aus Energiespargründen im Gegensatz zum ARM-Cortex-A9 oder Cortex-A15 keine Out-of-Order-Befehlsausführung, kann zwei Befehle gleichzeitig verarbeiten (Dual-Issue) und kommt mit einer 16-stufigen Pipeline ohne dediziertem Integer-Hardware-Multiplizierer oder -Dividierer daher (diese Funktionalität findet sich in dem Block für Gleitkommazahlen-Verarbeitung wieder). Es wird derselbe Befehlssatz wie beim Core-2 unterstützt, d.h. inklusive SSE3 und Intel-64-Instruktionen. Ergänzend zum 512 KB großen L2-Cache gibt es noch 256 KB Low-Power-SRAM, das auch eine eigene Spannungsversorgung aufweist . Wenn die CPU in den tiefsten C6 genannten Sleep-Modus übergeht, werden die CPU-Register und Teile des L2-Caches in dieses SRAM ausgelagert, wodurch die Spannungsversorgung am restlichen SoC heruntergefahren bzw. sogar ganz abgeschaltet werden kann (Power-Gating).

Entscheidend für die Batterielaufzeit ist letztendlich die Unterstützung für andere Sleep-Modi und deren Ausnutzung durch das Betriebssystem. Der sogenannte Linux-Governor von Android kann dafür die CPU-Taktfrequenz zur Laufzeit verändern. Laut Intel kann das SoC in 100-MHz-Schritten zwischen 100 MHz und 1,6 GHz getaktet werden (und natürlich im Status C6 bis auf das 256 KB große SRAM ganz abgeschaltet).

Tatsächlich verwendet der Android-Governor abgesehen vom Energiesparmodus C6 jedoch nur Taktfrequenzen von 600 MHz, 900 MHz, 1,2 GHz, 1,4 GHz und 1,6 GHz. Untersuchungen mit einer CPU-Spy genannten Andorid-App zeigen, dass das X900, wenn man es in der Hemdtasche mit sich trägt, wirklich jedesmal in den C6-Modus überführt wird. Telefongespräche, SMS-Versand und sogar Internet-Browsing bei entsprechend langsamer Datenübertrgung per 3G werden bei 600 MHz vorgenommen, nur bei extremer Belastung wie bei Spielen wird der Chip mit 1,6 GHz getaktet. Über die Gründe, warum keine Taktung unterhalb von 600 MHz implementiert wurde, kann man nur spekulieren: Vermutlich sind die Energieeinsparungen in Relation zu den Schlaf- und Aufweck-Aktivitäten nicht hoch genug.